# РАЗРАБОТКА ГЕНЕРАТОРА СИГНАЛОВ ПРОИЗВОЛЬНОЙ ФОРМЫ ТАБЛИЧНЫМ МЕТОДОМ В ПРОГРАММНОЙ СРЕДЕ QUARTUS

# Кусаинов Бахтияр Азаматович

студент, кафедра средства связи и информационная безопасность, Омский Государственный Технический университет, РФ, г. Омск

# Грачев Георгий Игоревич

студент, кафедра средства связи и информационная безопасность, Омский Государственный Технический университет, РФ, г. Омск

## DEVELOPMENT OF AN ARBITRARY-FORM SIGNAL GENERATOR BY A TABULAR

# Bakhtiyar Kusainov

Student, Department of Communications and Information Security, Omsk State Technical University, Russia, Omsk

# **Grachev George**

Student, Department of Communications and Information Security, Omsk State Technical University, Russia, Omsk

**Аннотация.** В данном курсовом проекте произведено разработка и проектирование устройства генерации сигнала табличным методом на ПЛИС при помощи программной среды Quartus на языке описания аппаратуры Verilog.

**Abstract**. In this course project, the development and design of a signal generation device by a tabular method on an FPGA using the Quartus software environment in the Verilog hardware description language was carried out.

**Ключевые слова:** Генератор, аналоговые сигналы, цифровые сигналы, ПЛИС, Quartus, Программируемая логическая интегральная схема, проектирование, Verilog.

**Keywords:** Generator, analog signals, digital signals, FPGA, Quartus, Programmable logic integrated circuit, design, Verilog.

Инновационные методы решения экологических проблем существуют.

В Verilog память – это массив регистров. Объявляется следующим образом: reg [7:0] mem\_name[1023:0]; «mem\_name» память, которая содержит 1024 ячеек, каждая ячейка состоит из 8-битного регистра.

Доступ к отдельной ячейке осуществляется так:  $dac1_d \le mem_name[124] - 8$ -ми битное значение из 124-ой ячейки записывается в 8- битный регистр dac1 d.

Доступ к отдельному биту ячейки осуществляется так: assign led[0] <= mem\_name[124][7] - Значение старшего (7-го) бита 124-ой ячейки назначается 0-му биту шины led.

Доступ к группе бит ячейки осуществляется так: assign led <= mem\_name[124][7:4] Значение четырех старших бит 124-ой назначается шине led.

Память может быть инициализирована начальными значениями с

помощью системных функций readmemh и readmemb. При компиляции проекта функции считывают значение из текстового файла и помещают их в указанную память. Файл для функции readmemh должен содержать данные в шестнадцатеричном формате, для функции readmemb - в двоичном.

Вызов функций должен происходить в блоке инициализации Inicial.

Общий синтаксис вызова следующий: \$readmemh ( " file\_name " , memory\_name [ , start\_addr [ , finish\_addr ] ] ); где file\_name - относительный путь к файлу и имя, memory\_name - имя инициализируемой памяти, start\_addr - начальный адрес для загрузки, finish\_addr - конечный адрес. Последние два параметра опциональны.

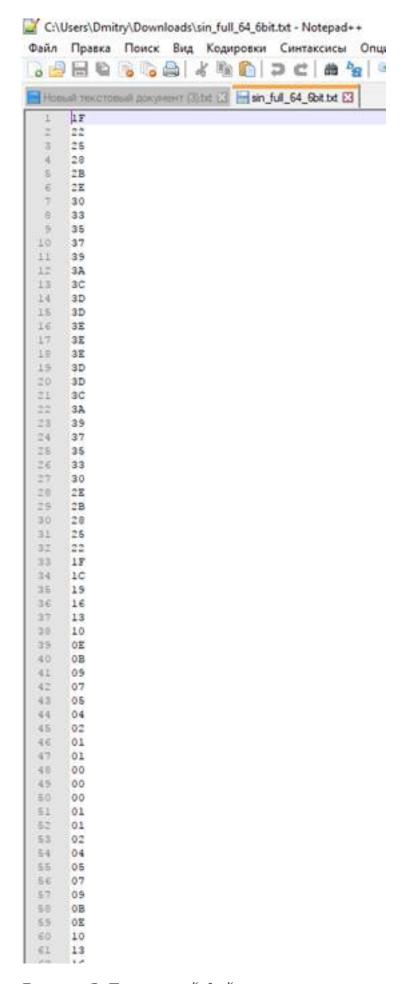

Программный код генератора, а также табличные значения в текстовом файле показаны на рисунке 1 и 2.

```

module course(clk_50MHz, dac1, dac2);

23

input clk_50MHz;

вход с тактового генератора

4

5

6

7

8

9

10

reg [13:0] dac1_d,

шина данных ЦАЛ1

dac2_d;

// Шина данных ЦАЛ2

output [13:0] dac1, dac2;

reg [5:0] rom_1[63:0];

объявляем ком. объем: 64 ячеек,

разрядность ячеек: 6бит.

инициируем память значениями из файла

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

27

initial

требуется указать путь к файлу с таблицей

0

begin

$readmemh("C:/Users/Dmitry/Downloads/sin_full_64_6bit.txt", rom_1);

reg [7:0] phase_acc_1;

// Регистр аккумулятора фазы

// фазовый аккумулятор

always @(posedge clk_50MHz)

phase_acc_1 <= phase_acc_1 + 1; // прибавляем код частоты

always @(posedge clk_50MHz)

begin

dac1_d <= {phase_acc_1[7:0], 6'h0}; // на ЦАП1 выводим значение фазы dac2_d <= {rom_1[phase_acc_1[7:0]], 6'h0}; // на ЦАП2 выводим сигнал

28

29

assign dac1 = dac1_d;

30

assign dac2 = dac2_d;

endmodule

31

```

Рисунок 1. Программный код генератора

Рисунок 2. Текстовый файл с значениями

На 11 строчке кода происходит чтение текстового файла, в котором записаны 64 отсчета по 6 бит. Данные значения заносятся 6 битный массив регистров rom 1 на 64 ячейки.

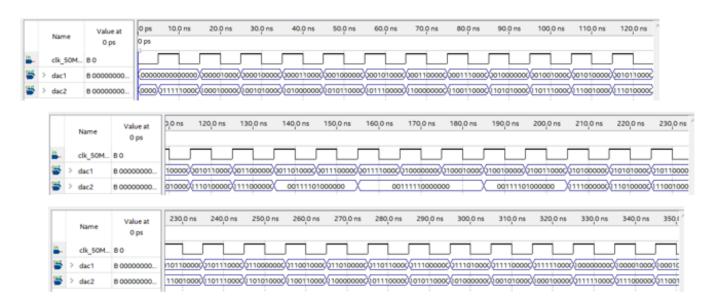

По каждому положительному перепаду генератора СLК происходит инкрементация регистра  $\phi$ азового аккумулятора, а также внесение в pегистры  $dac1_d$  и  $dac2_d$  значений. Регистр  $dac1_d$  формирует синусоидальный сигнал, dac2 d – пилообразный.

С помощью встроенных инструментов произведена симуляция проекта (рисунок 3).

Рисунок 3. Симуляция работы программы

#### Заключение

Генераторы сигнала являются неотъемлемой частью современной цифровой индустрии. В ходе выполнения курсового проекта были изучены различные способы генерации сигналов, а также виды генераторов.

В программной среде Quartus разработан работоспособный образец генератора сигнала табличным методом, задаваемый в отдельном текстовом файле. Устройство способно генерировать сигнал с 64 отсчетами на период с 6 битной точностью.

### Список литературы:

- 1. Берикашвили В.Ш. Электроника и микроэлектроника: импульсная и цифровая электроника, 2018 г. 188 с.

- 2. Википедия. Свободная энциклопедия [Электронный ресурс]. Режим доступа: URL

https://ru.wikipedia.org/wiki/Шифратор

- 3. Миловзоров О. В. Электроника, 2015 г.

- 4. Андык В.С. Автоматизированные системы управления технологическими процессами на ТЭС, 2018 г. 248 с.

- 5. Кузовкин В.А. Электротехника и электроника, 2018 г. 226 с.