Методы измерения временных параметров микросхем

Журнал: Научный журнал «Студенческий форум» выпуск №19(112)

Рубрика: Технические науки

Научный журнал «Студенческий форум» выпуск №19(112)

Методы измерения временных параметров микросхем

Аннотация. В статье рассматривается виды временных характеристик в цифровых устройствах. Каждая характеристика подробно описывается и рассматриваются методы измерения временных характеристик.

Ключевые слова: методы измерения, задержка, предустановка, время выдержки, временные характеристики.

В цифровых логических элементах есть множество характеристик, влияющих на принцип работы микросхемы. Например, чтобы согласовать множество логических элементов требуется знать временные характеристики данного устройства. Далее более подробно рассмотрим способы измерения временных характеристик.

Для правильной работы цифровых микросхем необходимо учитывать два временных параметра. Первый параметр, называемый время предустановки (Ts), указывает, как долго сигнал на входе от микросхемы должен оставаться стабильным до прихода фронта тактового сигнала. Второй параметр также показывает промежуток времени после прихода фронта синхросигнала (clk), гарантируя стабильность его на выходе. Этот параметр называется временем выдержки (Th)[1]. Выше описанные параметры показаны на рисунке 1.

Рисунок 1. Диаграмма предустановки (Ts) и выдержки (Th)

Кроме того, чтобы гарантировать работу различных элементов электронных устройств в заданной временной последовательности, нужно задержать появление на их входах исполнительных импульсов относительно задержано для установки Δt требуемого временного интервала. Этот временной интервал Δt = tз называется временем задержки. Функцию временной задержки электрического сигнала выполняют элементы задержки, условно графическое обозначение, диаграммы работы и схемы распределения импульсов показаны на рисунке 2.

Рисунок 2. УГО (а), временные диаграммы элемента задержки (б) и структурная схема распределителя импульсов (в)

Функциональный фрагмент электронного устройства называется элементом временной задержки (ЭВЗ), если импульс напряжения (сигнал) на выходе не возникает одновременно с появлением импульса на входе, а, например, возникает через равные промежутки времени tЗ – время задержки Δt.

Временная задержка используется очень широко. Например для схем развертки в электронных осциллографах, радиолокационном и гидроакустическом оборудовании; для селекции сигналов и так далее. Кроме того, для одних устройств необходимо сохранение формы задерживаемого сигнала, а в других достаточно скорректировать момент появления задержанного сигнала. Для некоторых устройств достаточно постоянного времени задержки, в то время как для других может потребоваться дискретная или плавная регулировка. Все это является причиной различных современных ЭВЗ, которые используют разные явления, принципы и методы для получения временных задержек[2].

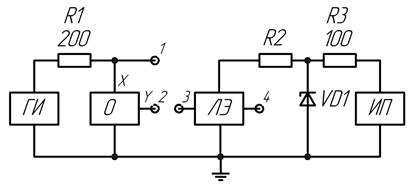

Поэтому было принято решение разработать схемы измерений этих параметров у цифровых электрических схем. Первая схема измерения задержки импульса представлена на рисунке 3.

Рисунок 3. Схема измерения временных задержек

Измерения происходят по следующему алгоритму:

1. Установить ток защиты 0,01 А и напряжение 10 В. Установить частоту генератора 100 кГц, длительность импульсов 0,5 мкс амплитуду 4 В, контролируя параметра импульсов с помощью осциллографа.

2. Соединить гнезда 1 и 2. Установить на осциллографе режим ждущей развертки и внешнего запуска от положительного перепада импульса запуска. Вращая ручку "Уровень" осциллографа, добиться устойчивого изображения фронте импульса при положении переключателя "Развертка.

3. Соединить с помощью перемычки гнездо 1 со входом элемента (гнездо 3), отметить положение середины фронта относительно делений координатной сетки экрана, переключить вход "Y " осциллографа со входа логического элемента на его выход (гнездо 4).

4. Определить время переключения логического элемента из состояния логической 1 в состояние логического 0, как смещение середины фронта импульса относительно своего первоначального положения.

5. Определить время переключения логического элемента из состояния логического 0 в состояние логической 1, установив режим запуска от отрицательного перепада импульса и повторив пункт 2 — 3.

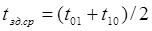

6. Определить значение среднего времени задержки по формуле 1 [1].

(1)

(1)

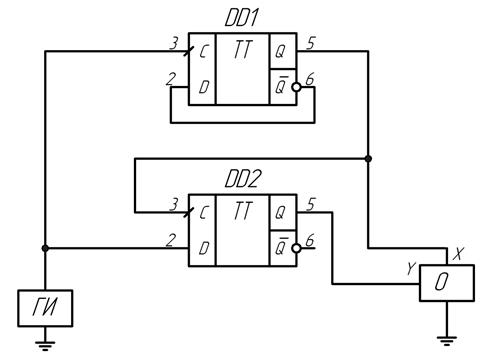

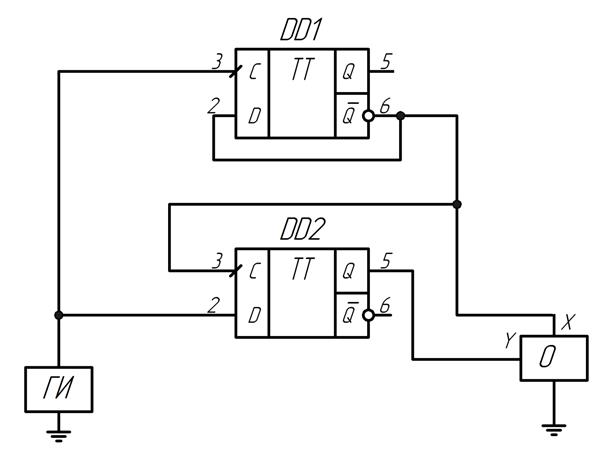

Вторая схема измерения показана на рисунке 4 для измерения времени предуставовки. Для измерения требуется генератор прямоугольных импульсов и осциллограф, по этой схеме можно определить максимальное время предустановки у логических элементов. Примерно такой же вид имеет и схема измерения выдержки, представленная на рисунке 5.

Рисунок 4. Схема измерения предустановки логического элемента

Рисунок 5. Схема измерения выдержки логического элемента

Описанные выше схемы представляют возможность изучать цифровые логические устройства на предмет определения у них основных временных параметров, а так же позволяет синхронизировать элементы между собой.