Проектирование генератора синусоидального тестового сигнала табличным способом на ПЛИС

Конференция: LXIV Студенческая международная научно-практическая конференция «Молодежный научный форум»

Секция: Технические науки

LXIV Студенческая международная научно-практическая конференция «Молодежный научный форум»

Проектирование генератора синусоидального тестового сигнала табличным способом на ПЛИС

DESIGNING A SINUSOIDAL TEST SIGNAL GENERATOR IN A TABULAR MANNER ON THE FPGA

Rustem Gabdullin

Student Omsk state technical University, Russia, Omsk

Аннотация. Синусоидальные, или гармонические, сигналы широко используются в электронике в качестве несущих и гетеродинных сигналов, в качестве тестовых сигналов при частотном анализе линейных схем, в качестве опорных сигналов в измерительных системах. В статье рассмотрен табличный способ проектирования генератора сигналов синусоидальной формы посредством использования программной среды «Quartus».

Abstract. Sinusoidal, or harmonic, signals are widely used in electronics as carrier and heterodyne signals, as test signals in frequency analysis of linear circuits, as reference signals in measurement systems. The article considers a tabular method of designing a sine wave signal generator by using the software environment "Quartus".

Ключевые слова: генератор, синусоидальный сигнал, программируемая логическая интегральная схема (ПЛИС), счетчик, постоянное запоминающее устройство.

Keywords: generator, sinusoidal signal, programmable logic integrated circuit (FPGA), counter, read-only memory.

Генератором синусоидальных колебаний называют устройство, создающее переменное синусоидальное напряжение при отсутствии входных сигналов [1]. Функциональная схема для цифрового генератора синусоидальных колебаний на основе памяти [2] изображена на рисунке 1.

Рисунок 1. Функциональная схема для цифрового генератора синусоидальных колебаний на основе памяти

Генератор тактовых импульсов обеспечивает формирование управляющих импульсов заданной частоты. Счетчик подсчитывает число импульсов, поступивших на его вход. Постоянное запоминающее устройство хранит массив неизменяемых данных, выдает текущее значение уровня сигнала на выходе. Цифро-аналоговый преобразователь преобразует цифровое значение уровня сигнала в аналоговый уровень сигнала. Буферное устройство обеспечивает необходимую амплитуду сигнала на выходе.

Тестирование генератора осуществлялось на отладочном комплекте DE1-SoC. Также для создания генератора использовалась программная среда «Quartus Prime». Программное обеспечение «Quartus» предоставляет полный цикл для создания высокопроизводительных систем [3] на кристалле. «Quartus» объединяет в себе проектирование, синтез, размещение элементов, трассировку соединений и верификацию, связь с системами проектирования других производителей.

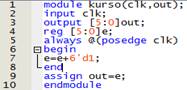

Для проектирования генератора в среде «Quartus» были созданы: командный алгоритм счетчика на языке «Verilog», блоки-элементы в графическом редакторе «Block Diagram/Schematic File».

Для проектировки счетчика необходимо разработать алгоритм на языке «Verilog». «Verilog HDL» (Hardware Description Language) - это язык текстового описания аппаратуры, предназначенный для проектирования, моделирования, верификации цифровых микросхем, плат и систем.

Рисунок 2. Verilog-модуль счетчика

Текст такой программы начинается с ключевого слова «module» и заканчивается ключевым словом «endmodule» [4]. После ключевого слова «module» пишется имя модуля, и в скобках указывается список выводов. В модуле имеются: «out» - выход счетчика; «clk» – тактовый вход; «input» – входной порт; «output [5:0]out» – 6-разрядный выходной порт; «reg [5:0]e» – 6-разрядный регистр (внутренняя переменная) «e»; «always @(posedge clk)» – поведенческий блок (в скобках указывается список всех входных сигналов, к которым чувствителен блок); «begin» - начало процесса; «e = e + 6’d1» – основа работы счетчика (к переменной прибавляется единица); «end» – конец процесса; «assign out = e» - непрерывное назначение, присваивание (“подключение” одной шины к другой). После написания модуля следует сохранить его («File/Save As»). Далее необходимо провести компиляцию (кнопка «Start Compilation»).

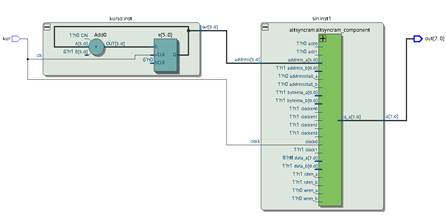

При успешной компиляции разрабатывается блок-схема. Создаются входы и выходы («input» и «output» соответственно). После размещения по полю графического редактора входного и выходного портов следует создать «ПЗУ ROM: 1-PORT», например, с параметрами: ширина шины - 8 бит, количество 8-битных слов в памяти - 64. Следует расположить блок ПЗУ в графическом редакторе. Для создания блока счетчика следует открыть созданный ранее файл «Verilog HDL», в левом верхнем углу открыть вкладку «File» и следовать по пути: «Create/ Update – Create Symbol Files foe Current File». Расставив все элементы в правильном порядке, необходимо соединить их. Для того чтобы сделать файл основным, выбираем пункт меню «Project/Set as Top-Level Entity». Проводится компиляция.

Рисунок 3. Схема генератора в среде «Quartus»

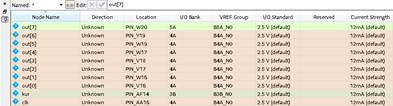

После компиляции необходимо назначить порты, и загрузить проект на отладочную плату. Назначение портов проводится по справочным данным в колонку «Location». После операции также проводится компиляция.

Рисунок 4. Таблица с данными портов

В основном окне «Quartus» выбираем утилиту «Program device (Open Programmer)». В утилите необходимо указать подключенное устройство, конфигурировать его и провести отладку нажатием на кнопку «Start». Проект успешно загрузился на отладочную плату.

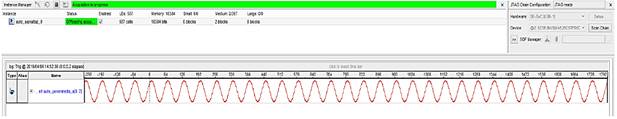

Заключительным этапом является работа с «SignalTap Logic Analyzer» - утилитой, которая позволяет посмотреть на временные диаграммы интересующих нас сигналов, генерируемых в микросхеме. В «Altera SignalTap Logic Analyzer» можно: добавить интересующие нас сигналы из разрабатываемого проекта; выбирать сигнал тактовой частоты для анализатора; выбирать сигнал, который будет служить триггером. После того, как все назначения сделаны, нужно сохранить файл «SignalTap» пользуясь его меню. Автоматически будет предложено подключить «SignalTap» к проекту.

После конфигурирования и сохранения весь проект нужно перекомпилировать. После компиляции проект будет занимать в микросхеме ПЛИС больше места. Проект занимает 587 элементов ПЛИС. Кроме того, занято 16384 бита памяти. Необходимо запустить анализатор «SignalTap» через меню «Processing / Run Analysis». Анализатор переходит в состояние ожидания события триггера.

Рисунок 5. Записанный синусоидальный сигнал

Генератор синусоидального сигнала спроектирован.

Подводя итог, можно сказать, что проект оказался достаточно работоспособен, генерация синусоидальных сигналов отлажена. При самой же разработке генератора синусоидальных сигналов в среде «Altera Quartus Prime» использовалось достаточное большое количество утилит. Использование программных сред является оптимальным решением в мире современных технологий.