Разработка конструкции и маршрута изготовления КМОП интегральной схемы восьмиразрядного стека памяти на базе DV-триггера

Конференция: XII Международная научно-практическая конференция «Научный форум: технические и физико-математические науки»

Секция: Электроника

XII Международная научно-практическая конференция «Научный форум: технические и физико-математические науки»

Разработка конструкции и маршрута изготовления КМОП интегральной схемы восьмиразрядного стека памяти на базе DV-триггера

DESIGN OF CONSTRUCTION AND MANUFACTURING ROUTE OF CMOS INTEGRATED CIRCUIT OF EIGHT-BIT MEMORY STACK BASED ON DV-FLIP-FLOP

Leonid Nedashkovskiy

Master’s Degree student of National Research University of Electronic Technology, Russia, Moscow

Аннотация. В статье представлены основные этапы комплексной разработки цифровой интегральной схемы восьмиразрядного стека памяти на базе DV-триггера на логическом, схемотехническом (транзисторном) и топологическом уровнях. Приведены результаты исследования и разработки технологического маршрута изготовления КМОП-структур, на которых основана схема. Подсчитаны основные характеристики и параметры устройства, а также показаны результаты моделирования. Проведён анализ выбора ширин транзисторов.

Abstract. The article presents the main stages of complex design of digital integrated circuit of eight-bit memory stack based on DV-flip-flop at the logical, schematic (transistor) and layout levels. The results of research and design of the technological route for manufacturing CMOS structures on which the scheme is based are presented. The main characteristics and parameters of the device are calculated, and the simulation results are shown. The analysis of transistors widths choice is carried out.

Ключевые слова: КМОП, моделирование, Microwind, OrCAD, последовательная логика, схемотехника, TCAD, цифровое проектирование, цифровые интегральные схемы, электроника, электронная компонентная база.

Keywords: CMOS, simulation, Microwind, OrCAD, sequential logic, circuit engineering, TCAD, digital design, digital integrated circuits, electronics, electronic component base.

Введение

Микросхемы памяти в общем объёме выпуска интегральных схем (ИС) занимают около 40% и играют важнейшую роль во многих системах различного назначения [1].

Существует множество различных типов запоминающих устройств (ЗУ) в зависимости от способа доступа к данным, организации хранения информации. В данной работе рассматривается стековый тип памяти. Это разновидность полупроводниковых ЗУ с последовательным доступом; является частью энергозависимой оперативной памяти. Стек представляет собой одномерный массив ячеек памяти, в котором информация обрабатывается побитно, «поочерёдно». Причём если запись информации идёт в прямом порядке, то считывание – в обратном. Такой способ организации данных называется LIFO (Last In – First Out) – «последним ушёл – первым пришёл».

В универсальных микропроцессорах стек и стековая адресация используются для временного хранения данных, при организации переходов к подпрограммам и возврате из них, а также при обработке прерываний. Стек удобен тем, что нет необходимости хранить адрес каждого бита.

Работа посвящена проектированию восьмиразрядного стека памяти на триггерах по технологии КМОП (комплиментарная структура металл-оксид-полупроводник). Мировое производство полупроводниковых изделий в своей подавляющей части основано на конструктивно-технологическом базисе комплиментарных МОП (КМОП) приборов [2]. Именно по такой технологии изготавливается большинство современных логических микросхем, в том числе процессоров, потому что она обеспечивает высокое быстродействие и наименьшее потребление мощности.

Также в данной работе разрабатывается и исследуется технологический маршрут создания n- и p-канальных МОП-транзисторов в составе КМОП-структуры. Оптимизация технологических процессов изготовления элементов ИС играет важную роль в микроэлектронном производстве, потому что параметры каждого этапа непосредственно влияют на электрические, топологические и функциональные характеристики устройства.

Общие сведения о стеке памяти

По способу доступа к данным ЗУ делятся на адресные, ассоциативные и последовательные. В ЗУ с последовательным доступом записываемые данные образуют некоторую очередь. Считывание происходит из очереди слово за словом либо в порядке записи, либо в обратном порядке. Моделью такого ЗУ является последовательная цепочка запоминающих элементов, в которой данные передаются между соседними элементами [1].

Классический пример ЗУ последовательного типа – это регистры [3]. Прямой порядок считывания имеет место в буферах FIFO с дисциплиной «первый пришёл – первый вышел» (First In – First Out), а также в файловых и циклических ЗУ. Считывание в обратном порядке свойственно стековым ЗУ, для которых реализуется дисциплина «последний пришёл – первый вышел». Такие ЗУ называют буферами LIFO [1]. Также представителем данного вида памяти является видеопамять.

Использование принципа доступа к памяти на основе механизма LIFO началось с больших ЭВМ. Применение стековой памяти оказалось очень эффективным при построении компилирующих и интерпретирующих программ, при вычислении арифметических выражений с использованием польской инверсной записи. В малых ЭВМ она стала широко использоваться в связи с удобствами реализации процедур вызова подпрограмм и при обработке прерываний [4].

Стек LIFO по порядку записи-считывания подобен стопке тарелок – для использования снимается верхняя, т.е. последняя положенная, затем вторая и т.д. Интересно отметить, что сам термин «стек» (stack) произошёл именно от обозначения такой стопки [3]. В 1946 Алан Тьюринг ввёл понятие стека. А в 1957 году немцы Клаус Самельсон и Фридрих Л. Бауэр запатентовали идею Тьюринга.

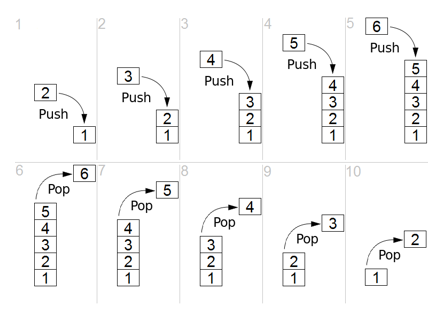

Стек имеет дно и верхушку, направление возрастания номеров ячеек в нём может быть различным (обычный и перевёрнутый стеки). Операции со стеком – PUSH (запись слова) и POP (считывание слова) [3]. Принцип работы стека изображён на рисунке 1.

Рисунок 1. Организация стека в виде одномерного упорядоченного по адресам массива. Показаны операции вталкивания и выталкивания данных из стека операциями push и pop

Наиболее распространенным в настоящее время и, возможно, лучшим вариантом организации стека в ЭВМ является использование области памяти [4]. При этом данные в стеке не сдвигаются: каждый бит записывается в свою отдельную ячейку памяти. В данной работе разрабатывается именно этот тип стека.

Аппаратно такой стек реализуется в оперативных ЗУ (ОЗУ), где для него выделяется определённая область. Указатель стека SP (Stack Pointer) содержит адрес последней занятой ячейки.

Описание логики устройства

На этапе логического проектирования приводятся описание элементов, входящих в состав его структуры, на вентильном уровне, а также результаты моделирования элементов в программе PSpice Schematics, входящей в состав САПР OrCAD 16.5.

Схематичное устройство восьмиразрядного стека LIFO, использующего выделенную область памяти, представлено на рисунке 2.

Рисунок 2. Состав восьмиразрядного стека памяти

Основу данного стека составляют пять функциональных блоков:

1) блок, обеспечивающий двунаправленность порта данных INPUT-OUTPUT PORT;

2) нецикличный реверсивный счётчик от 0 до 8 REVERSIBLE COUNTER 0‑8;

3) дешифратор из 4 в 8 DECODER FROM 4 TO 8;

4) восьмиразрядный элемент памяти MEMORY ELEMENT 8-BIT;

5) мультиплексор из 8 в 1 MULTIPLECSOR FROM 8 TO 1.

Устройство может работать в одном из трёх режимов: запись (PUSH), считывание (POP) и хранение. Режим задаётся комбинацией двух сигналов: Record и Read (таблица 1).

Таблица 1.

Режимы работы стека памяти

|

Record |

Read |

Режим |

|

0 |

0 |

Хранение |

|

0 |

1 |

Считывание |

|

1 |

0 |

Запись |

|

1 |

1 |

Хранение |

В режиме записи данные Data поступают через двунаправленный порт в элемент памяти и записываются в определённую ячейку (триггер), согласно указателю старшей свободной ячейки. В режиме хранения данные в ячейке памяти и указатель не меняются. В режиме считывания данные побитно поступают на двунаправленный порт.

Указатель S[3:0] представляет собой четырёхразрядное число, формируемое счётчиком. Если значение указателя «0», стек пуст, считывать нечего, «включается» флаг пустоты M_0. При значении указателя «8» активизируется флаг переполнения M_8, указывающий на то, что записывать информацию некуда. В таких случаях стек переходит в режим хранения информации.

Во время записи дешифратор посылает сигнал разрешения переключения V[7:0] на ячейку памяти, согласно значению указателя S[3:0]. Так обеспечивается поочерёдная запись данных. Во время считывания мультиплексор подаёт на выход информацию с той ячейки, на которую направляет всё тот же указатель. Стоит отметить, что при считывании информация в элементе памяти не стирается, а сохраняется до тех пор, пока не произойдёт запись новой информации или полный сбор стека сигналом Reset.

Элемент памяти и счётчик построены на синхронных DV-триггерах типа «Master-Slave», причём в схемотехническом и топологическом проектировании они заменяются двухтактными триггерами на проходных ключах (ПК) [5] в целях уменьшения максимального логического пути и площади на топологии.

Восьмиразрядный элемент памяти представляет собой совокупность восьми DV-триггеров, не связанных друг с другом. Ко входам данных всех триггеров подключена общая шина данных, информация с которой записывается в тот триггер, для которого разрешающий сигнал V = 1.

Значение указателя формируется в нецикличном реверсивном счётчике от 0 до 8. Все возможные значения указателя в разных ситуациях представлены в таблице 2.

Таблица 2.

Адресуемые указателем ячейки

|

Знач. ук.

Режим |

0 (0000) |

1 (0001) |

2 (0010) |

3 (0011) |

4 (0100) |

5 (0101) |

6 (0110) |

7 (0111) |

8 (1000) |

|

Запись |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

– |

|

Чтение |

– |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

Реверсивность обеспечивают сигналы Record и Read.

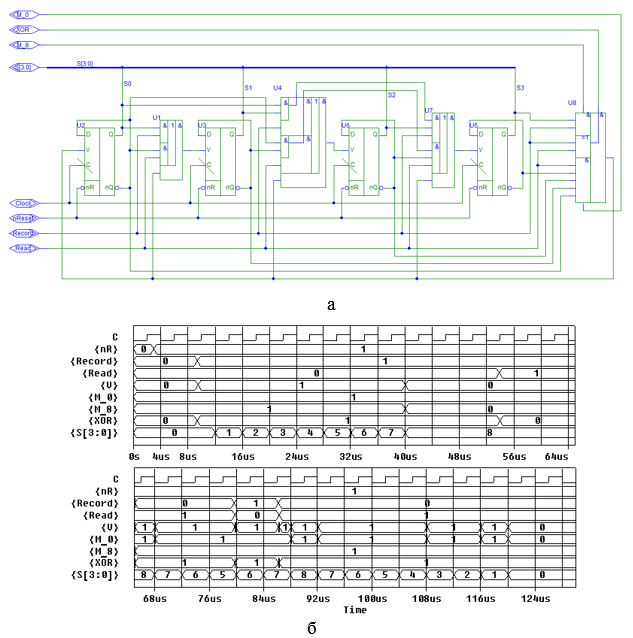

Логическая схема счётчика и результаты его моделирования показаны на рисунке 3.

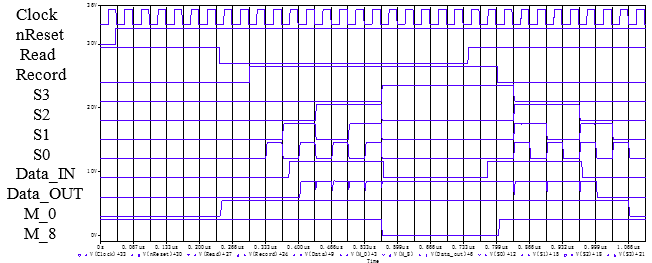

Результаты выборочного моделирования восьмиразрядного стека памяти представлены на рисунке 4. Из него видно, что в предварительно сброшенный (обнулённый) стек записывается число 101110112, хранится и затем считывается в порядке, обратном тому порядку, в котором записывалось это число.

Рисунок 3. Нецикличный реверсивный счётчик: а – структура; б – результаты моделирования

Максимальный путь, равный 13 вентилям, проходит синхросигнал (через Slave-ячейку триггера, мультиплексор и порт обеспечения двунаправленности).

Максимальный коэффициент разветвления, равный 8, наблюдается, например, в дешифраторе на выходе инвертированного сигнала S3.

Рисунок 4. Результаты выборочного моделирования восьмиразрядного стека памяти: записывается, хранится и считывается число 101110112

Схемотехническое проектирование

На этапе схемотехнического проектирования разрабатывается общая для всего проекта символьная библиотека необходимых логических вентилей на уровне транзисторов, подбираются необходимые параметры транзисторов, определяются частотные характеристики устройства, а также проводится полное схемотехническое моделирование всего устройства в программе PSpice Schematics. Также определяются минимальное напряжение питания и максимальная нагрузочная ёмкость, при которых характеристики устройства не выходят за рамки технических требований.

Устройство построено на шести элементах: НЕ, 2И-НЕ, 3И-НЕ, XOR на проходных ключах (ПК), DV-триггер на ПК и буфер с третьим состоянием. Буфер обеспечивает заданное быстродействие при работе на большую выходную нагрузочную ёмкость микросхемы и ставится на каждый выход схемы.

НЕ, 2И-НЕ, 3И-НЕ представляют собой известные базовые КМОП-схемы.

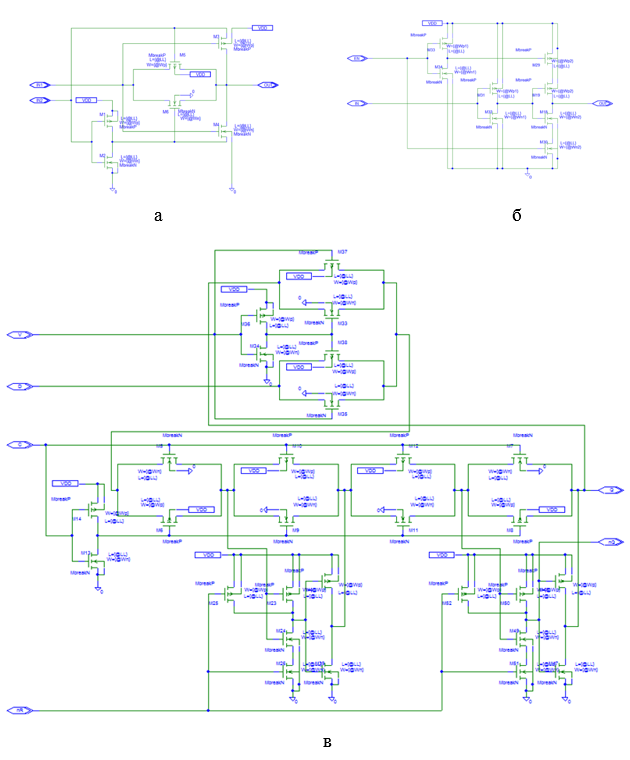

Схемы XOR и DV-триггера с использованием ПК, а также схема буфера с третьим состоянием представлены на рисунке 5.

Рисунок 5. Электрические схемы XOR (а), буфера с третьим состоянием (б), DV-триггера (в)

Ширина n-МОП-транзистора принимается минимально допустимой, а ширина p-МОП-транзистора вычисляется из условия равенства удельных крутизн и с учётом типа соединения транзисторов. Если не выравнивать крутизны, помехозащищённость логических уровней становится разной, потому что смещается точка переключения передаточной характеристики.

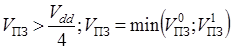

Условие возможности использования элемента с невыравненными крутизнами (1):

|

|

(1) |

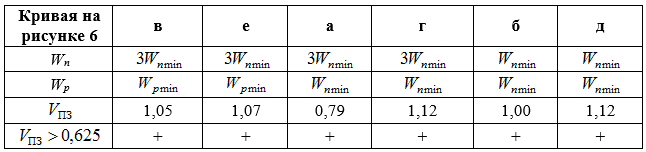

Передаточные характеристики элемента 3И-НЕ представлены на рисунке 6. Результаты моделирования при разных ширинах p-МОП-транзистора в разных случаях представлены в таблице 3.

Рисунок 6. Передаточные характеристики элемента 3И-НЕ

Случаи в, а, б соответствуют включению по наихудшему случаю по крутизне (открыт только один транзистор одного типа), а случаи е, г, д – по наилучшему случаю (открыты все транзисторы).

Исходя из полученных результатов, можно сделать вывод, что любая ширина p-МДПТ из вышеперечисленных допустима. Поэтому в дальнейшем ширины всех транзисторов всех элементов берутся равными минимально возможной.

Таблица 3.

Характеристики элемента 3И-НЕ с разными ширинами p‑МОП‑транзистора в наилучшем и наихудшем случаях

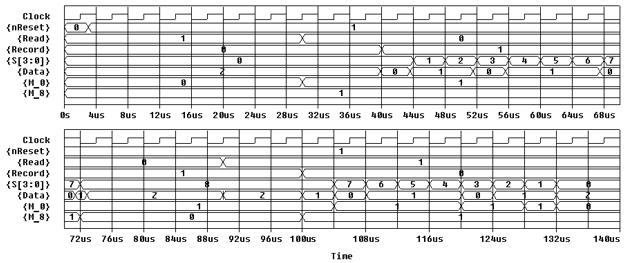

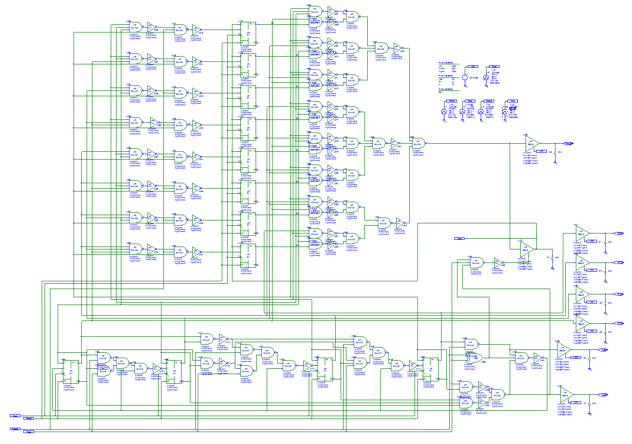

Схема устройства на библиотечных вентилях представлена на рисунке 7.

Рисунок 7. Общая электрическая схема устройства на библиотечных элементах

На рисунке 8 приведены результаты схемотехнического моделирования устройства, изображённого на рисунке 7. Эти результаты полностью идентичны результатам, полученным на этапе логического моделирования. Это свидетельствует о том, что устройство собрано правильно и работает корректно.

Рисунок 8. Результаты моделирования устройства в схемотехническом проектировании: записывается, хранится и считывается число 111111002

Основные результаты схемотехнического проектирования:

· длина транзисторов: 0,25 мкм;

· ширина транзисторов: 0,6 мкм;

· предельная частота работы устройства: 800 МГц;

· максимальная рабочая частота устройства: 118 МГц;

· максимальная нагрузочная способность инвертора: 31;

· средняя потребляемая мощность: 0,8 мВт;

· времена фронта и среза: 2 нс;

· общее количество транзисторов: 774.

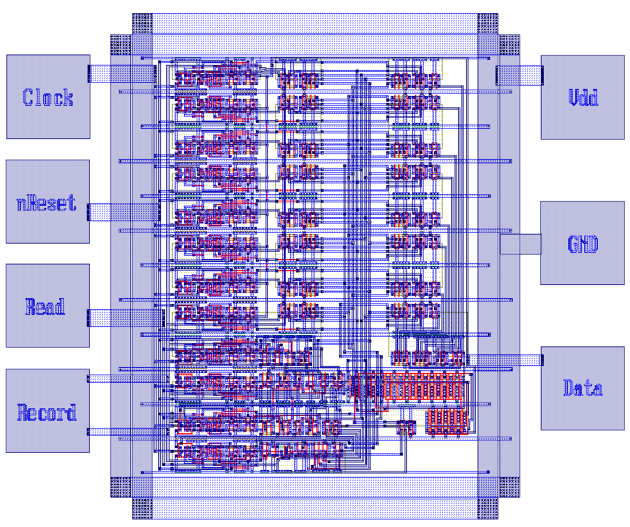

Топологическое проектирование

Топологическое описание интегральной микросхемы, или топология микросхемы – это двумерное многослойное изображение, включающее топологическое описание каждого маскирующего слоя, используемого в данном технологическом маршруте [6]. Проще говоря, это вид сверху на микросхему. По-другому, топология – набор масок для производства фотошаблонов, которые в свою очередь применяются в процессах фотолитографии при производстве интегральной схемы.

На этапе топологического проектирования создаётся библиотека топологических ячеек, из которых собирается топология полного устройства. Полученная топология моделируется с учётом паразитных элементов. Работа проводится в топологическом редакторе Microwind2.

Топология полностью собранного устройства представлена на рисунке 9. Она полностью соответствует требованиям правил проектирования DRC и соответствует электрической схеме. К выходам подключены буферные элементы и нагрузочные ёмкости.

Топология собрана для технологического КМОП-процесса CMOS-0.25um. Площадь, занимаемая на кристалле: 222×182 мкм2 = 0,04 мм2. Разводка выполнена первым и вторым слоями металлизации.

Рисунок 9. Топология полного устройства

Технологический маршрут изготовления КМОП-структуры

Технологический маршрут изготовления КМОП-структуры (рисунок 10) представляет собой последовательность технологических операций, необходимых для формирования интегральных n- и p-канальных транзисторов, области изоляции и металлизации.

Рисунок 10. Эскиз поперечного сечения КМОП-структуры после формирования металлизации, изолирующего слоя и вскрытия контактных окон (финальные стадии)

Полный маршрут создания КМОП-структуры с n+-затвором, n- и p-карманами и изоляцией LOCOS (локальное окисление кремния) со всеми необходимыми операциями и их режимами составляет около 80 операций. Весь маршрут условно разделяется на 5 этапов. При помощи программы Sentaurus Process, входящей в состав системы приборно-технологического моделирования Synopsys TCAD, проведено моделирование основных технологических операций при вариации определённых конструктивно-технологических параметров. Таким образом, определены примерные режимы для технологических операций (таблица 4).

Таблица 4.

Отдельные технологические маршруты формирования n- и p‑МОП‑транзисторов в составе КМОП-структуры c LOCOS-изоляцией и двумя n+-Si* затворами

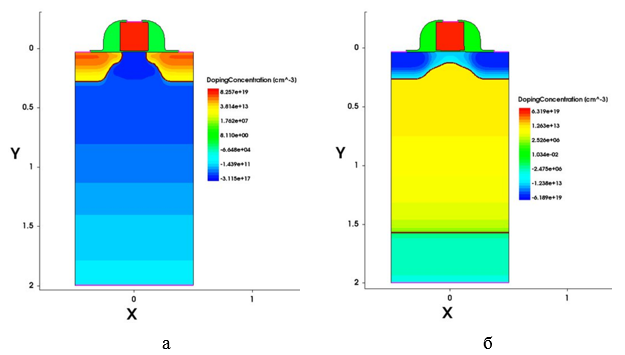

Полные двумерные модели МОП-транзисторов представлены на рисунке 11.

Рисунок 11. Результирующее распределение примеси (NetActive) в двумерных моделях n-МОП-транзистора (а) и p-МОП-транзистора (б)

Семейства выходных ВАХ таких транзисторов представлены на рисунке 12.

Рисунок 12. Семейства выходных ВАХ n-МОП-транзистора (а) и p-МОП-транзистора (б)

Заключение

Разработанное устройство удовлетворяет всем необходимым требованиям. С логической точки зрения данный прибор является универсальным, с топологической – законченным. Это значит, что его можно использовать как элемент более сложных микропроцессорных устройств. Основные принципы, изложенные в работе, могут быть полезны при проектировании элементов памяти и для понимания основ последовательной логики. Приведённая информация демонстрирует тесную взаимосвязь между проектированием и технологией изделий электронной техники.

.

.