РАЗРАБОТКА УСТРОЙСТВА ЗАДЕРЖКИ СИГНАЛОВ С ИЗМЕНЯЕМОЙ ДЛИТЕЛЬНОСТЬЮ ЗАДЕРЖКИ В ПРОГРАММНОЙ СРЕДЕ QUARTUS

Журнал: Научный журнал «Студенческий форум» выпуск №43(179)

Рубрика: Технические науки

Научный журнал «Студенческий форум» выпуск №43(179)

РАЗРАБОТКА УСТРОЙСТВА ЗАДЕРЖКИ СИГНАЛОВ С ИЗМЕНЯЕМОЙ ДЛИТЕЛЬНОСТЬЮ ЗАДЕРЖКИ В ПРОГРАММНОЙ СРЕДЕ QUARTUS

DEVELOPMENT OF A SIGNAL DELAY DEVICE WITH A VARIABLE DELAY DURATION IN THE QUARTUS SOFTWARE ENVIRONMENT

Henrik Miskarian

Student, Department of Communications and Information Security, Omsk State Technical University, Russia, Omsk

Denis Pyatkov

Department of Communications and Information Security, Omsk State Technical University, Russia, Omsk

Аннотация. В данном курсовом проекте произведено разработка и проектирование устройства генерации сигнала табличным методом на ПЛИС при помощи программной среды Quartus на языке описания аппаратуры Verilog.

Abstract. In this course project, the development and design of a signal generation device by a tabular method on an FPGA using the Quartus software environment in the Verilog hardware description language was carried out.

Ключевые слова: Линия задержки, электромагнитные волны, акустические волны, цифровая обработка сигнала, обработка аналоговых сигналов, ПЛИС, проектирование устройств, Quartus.

Keywords: Delay line, electromagnetic waves, acoustic waves, digital signal processing, analog signal processing, FPGA, device design, Quartus.

Задание: Разработать устройство линии задержки, имеющего 7-ми битный вход. Время задержки задано условием: если на входе число меньше 42 – задержка на 3 такта, от 42 до 84 – 5 тактов, больше 84 – 10 тактов.

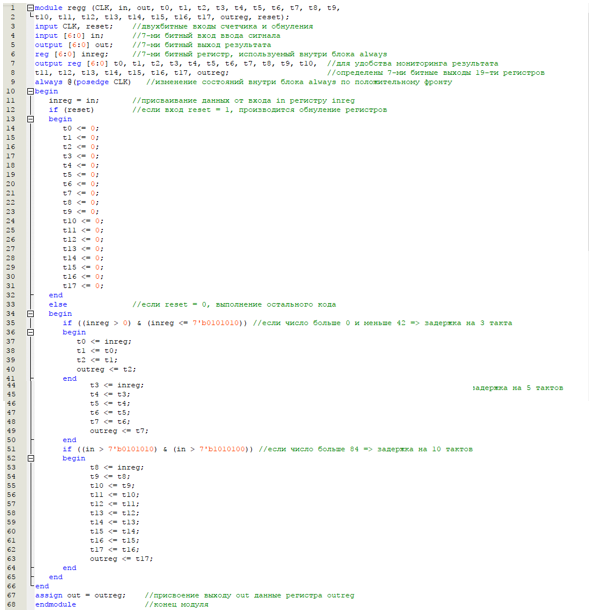

Программный код разработанного устройства представлен на рисунке 1.

Рисунок 1. Программный код устройства

Принцип работы устройства основан на использовании неблокирующего присваивания (в языке Verilog обозначается символом <=) и большого числа регистров, между которыми будет передаваться сигнал. Передача сигнала синхронизирована с положительным фронтом тактового CLK (в программе используется частота 50 МГц). Для наглядности работы ЛЗ используются output регистры, названия которых также указываются в списке портов. Также добавлен битовый вход reset, который очищает содержимое регистров (происходит обнуление) для исключения неисправности работы.

Неблокирующее присваивание изменяется в зависимости от блока always. В данном случае каждое присваивание происходит по положительному фронту тактового сигнала.

При подаче на вход in сигнала, устройство присваивает данное значение регистру inreg, после чего проверяет условия три условия if на истинность, где определяет, к какому диапазону чисел относится введенное число. Затем, если условие истинное, происходит неблокирующее присваивание содержимого регистра inreg сначала первому регистру, затем второму и т.д до последнего регистра outreg.

Количество строк присваивания на 1 больше, чем заданное количество тактов задержки, т.к. первое присваивание происходит мгновенно без задержки на такт.

После выполнения действий внутри блока if, происходит присваивание значения регистра outreg порту out.

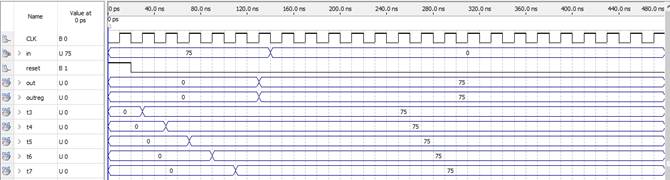

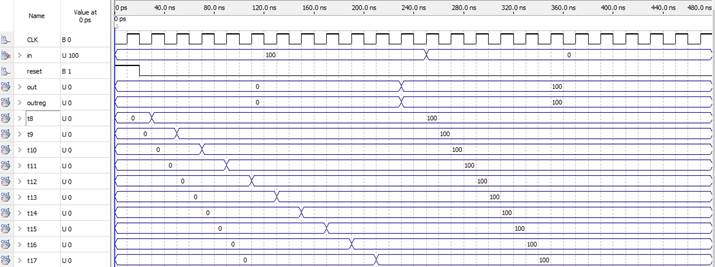

Работа программы продемонстрирована на рисунках 2 – 4. На вход in поданы числа 30, 75 и 100. Согласно коду, происходит задержка на 3, 5 и 10 тактов соответственно.

Рисунок 2. Число 30 задержано на 3 такта

Рисунок 3. Число 75 задержано на 5 тактов

Рисунок 4. Число 100 задержано на 10 тактов

Проанализировав результаты симуляции, видно, что задержка сигналов происходит согласно заданному принципу.

Заключение

Линия задержки является распространенным устройством для согласования или разнесения сигналов по времени или фазе. Область применения довольно широка – от телевидения до акустических инструментов. В ходе выполнения курсовой работы в программной среде Quartus была разработана линия задержки 7-ми битного сигнала на изменяемое количество тактов. Финальное устройство имеет один 7-ми битный вход для ввода задерживаемого сигнала, один битовый вход для обнуления регистров, один битовый вход для тактовых импульсов и один 7-ми битный выход.