РАЗРАБОТКА И РЕАЛИЗАЦИЯ УСТРОЙСТВА СЧЕТЧИКА В КОДЕ ГРЕЯ

Журнал: Научный журнал «Студенческий форум» выпуск №43(179)

Рубрика: Технические науки

Научный журнал «Студенческий форум» выпуск №43(179)

РАЗРАБОТКА И РЕАЛИЗАЦИЯ УСТРОЙСТВА СЧЕТЧИКА В КОДЕ ГРЕЯ

DEVELOPMENT OF A SIGNAL DELAY DEVICE WITH A VARIABLE DELAY DURATION IN THE QUARTUS SOFTWARE ENVIRONMENT

Arseniy Manushkin

Student, Department of Communications and Information Security, Omsk State Technical University, Russia, Omsk

Аннотация. В данной статье проведено проектирование устройства поиска среднего арифметического с выводом на семисегментный дисплей.

Abstract. In this article, the design of an arithmetic mean search device with output to a seven-segment display was carried out.

Ключевые слова: Ключевые слова: Счетчик, Код Грея, Quartus, Программируемая логическая матрица, Программируемая логическая интегральная схема, Проектирование, Структурная схема.

Keywords: Keywords: Counter, Gray Code, Quartus, Programmable logic matrix, Programmable logic integrated circuit, Design, Block diagram.

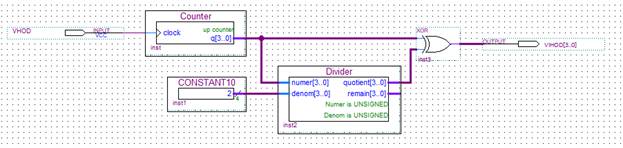

Разработку устройства будем вести в графическом редакторе программной среды Quartus. Проектирование схемы начнем с создания проекта. После создания проекта, создаем «Block Diagram/Schematic File», данная графическая среда позволит создать нам счетчик в коде Грея.

Для выполнения настоящей работы будем пользоваться библиотекой IP компонентов, которую вызовем комбинацией клавиш «Alt+7». В данной библиотеке нам понадобятся такие IP-компоненты, как «LPM_COUNTER» (счетчик в бинарном коде), «LPM_CONSTANT» (блок, на выходе которого постоянно число «10»), «LPM_DIVIDE» (делитель). Также в нашей схеме понадобится такой базовый логический элемент «XOR» (Исключающее-ИЛИ).

Спроектированная и скомпилированная схема представлена на рисунке 1.

Рисунок 1. Смоделированная схема счетчика в коде Грея в среде QUARTUS PRIME

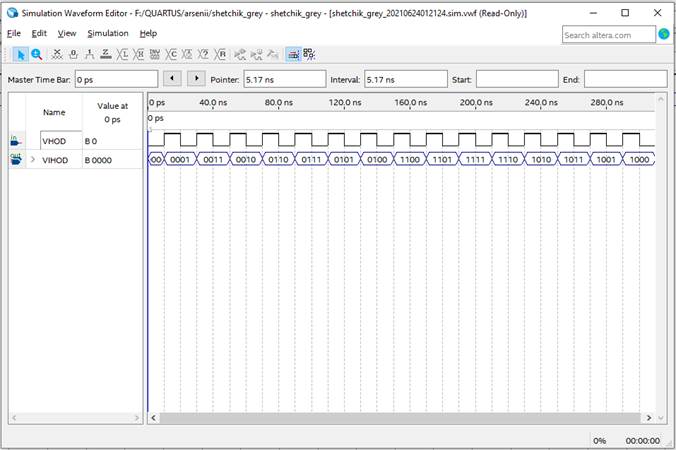

Теперь работоспособность настоящего проекта проверим с помощью функционального моделирования. Его результаты приведены на рисунке 2.

Рисунок 2. Функциональное моделирование спроектированного устройства – счетчика в коде Грея

Результаты, полученные в ходе функционального моделирования, удовлетворяют значениям кода Грея, представленным на рисунке 1, следовательно, схема собрана успешно и работает верно.

ЗАКЛЮЧЕНИЕ

В ходе выполнения курсовой работы мы разработали и спроектировали схему 4-х битного счетчика в коде Грея, изучили его принцип работы, а также проверили его работоспособность с помощью функционального моделирования. Полученный результат оказался успешным.

Данная схема способна считать 16 тактов в коде Грея. 4-х битное устройство – не предел. Максимальное число, которое может посчитать счетчик можно увеличить, повысив разрядность, используемого в схеме бинарного счетчика и делителя.

Спроектированная модель устройства работоспособна и полностью соответствует таблице кода Грея, что означает, что разработанная программа верна.