Библиотечные элементы Logisim, делитель частоты, их создание

Секция: Технические науки

лауреатов

участников

лауреатов

участников

XLIV Студенческая международная заочная научно-практическая конференция «Молодежный научный форум: технические и математические науки»

Библиотечные элементы Logisim, делитель частоты, их создание

В данной статье производится разбор последовательности шагов, приводящих к созданию библиотечных элементов в системе автоматизированного проектирования Logisim. В качестве опорного примера было взято построение делителя частоты с посмощью RS-триггеров, добавленное выводом значений на семисегментный индикатор.

Таким образом, по окончанию статью будет синтезирована цифровая схема с памятью.

Принцип работы схемы был выбран следующий: поступающая на вход схемы тактовая частота делится 3 раза на 10 с помощью трёх двоично-десятичных счётчиков, в совокупности образуя счётчик до 999, но на работу этих трёх двоично-десятичных счетчиков накладывается условие сброса в исходное состояние по достижению 186, что представляет собой делитель частоты на 186 (каждый двоично-десятичный счётчик реализован на основе четырёх RS-триггеров). Далее с выходов счётчиков сигналы поступают на кодер (декодер), осуществляющий преобразование входных сигналов, отождествляющих двоичное число, в выходные сигналы, ассоциированные с сегментами панели семисегментника.

Синтез двоично-десятичного счётчика:

Как было сказано выше, данный вид счётчика реализуется на базе 4-х RS-триггеров, соединенных последовательно из «Q» в «C». По сути, объединением входа S и инверсии, предшествующей входу R, мы переходим от RS-триггера к D-триггеру, а закорачиванием выхода инверсного Q с входом S, получаем T-триггер, реализация счётчика на котором довольно проста [2, с. 214].

Соединив последовательно 4 T-триггера, получаем двоичный счётчик, реализовав на его выходах минтерм 1010 (![]() ) и осуществив по нему сброс всех триггеров в нуль, имеем двоично-десятичный счётчик. Но так как мы снимаем разряды с инверсных выходов, то и сбрасываем не в нуль, а в единицу.

) и осуществив по нему сброс всех триггеров в нуль, имеем двоично-десятичный счётчик. Но так как мы снимаем разряды с инверсных выходов, то и сбрасываем не в нуль, а в единицу.

Синтезированная схема двоично-десятичного счётчика в Logisim представлена на рисунке 1.

Рисунок 1. Схема двоично-десятичного счётчика

Вход F0: необходимость в нем возникла в связи с тем, что требуется извне устанавливать выходы Q всех триггеров в единицу, то есть сбрасывать все разряды в нуль. F0 соединен по логическому «ИЛИ» с выходом элемента «И», реализующего минтерм сброса на десятом такте. Примечание: у каждого RS-триггера в Logisim имеется отдельный вход, положительный сигнал, поданный на который, установит на прямом выходе единицу, т.е. мы работаем не через set/reset.

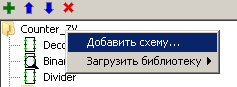

Теперь создадим библиотечный элемент Logisim с названием “Binary-decimal counter” на базе схемы, описанной выше. Для этого, кликнув ПКМ по проекту в Logisim, выбираем «добавить схему» (рис. 2), именуем и переносим в неё нашу схему.

Рисунок 2. Добавление схемы

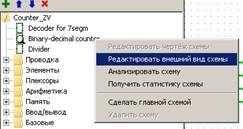

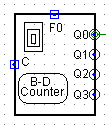

После этого кликаем ПКМ по нашей схеме в обозревателе элементов и выбираем «Редактировать внешний вид схемы» (рис. 3). Далее с помощью предлагаемых инструментов редактируем внешний вид, приводя элемент к форме удобного использования (рис. 4): растягиваем границы, перемещаем контакты, добавляем текст и окантовки.

Рисунок 3. Переход к редактированию внешнего вида

Рисунок 4. Внешний вид элемента «Д-Д счётчика»

Библиотечный элемент «Binary-decimal counter» готов.

Синтез кодера для семисегментника:

Исходным материалом для синтеза данного кодера является таблица истинности функций каждого входа семисегментника на наборах переменных в десятичном представлении от 0 до 9 [1, с. 258].

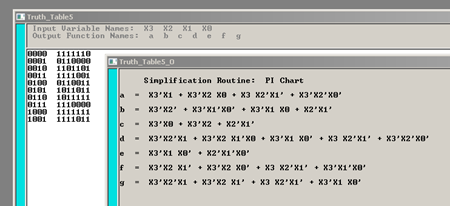

Для минимизации каждой функции по таблице истинности применим САПР LogicAid, в котором для внесения таблицы необходимо пройти по вкладке input, выбрать truth table, затем внести число функций, а их у нас 7, ввести имена. Далее вносим данные из исходной таблицы истинности в truth table LogicAid, выбираем Routine – Simplification – Ok, имеем все входные минимизированные функции (рис. 5).

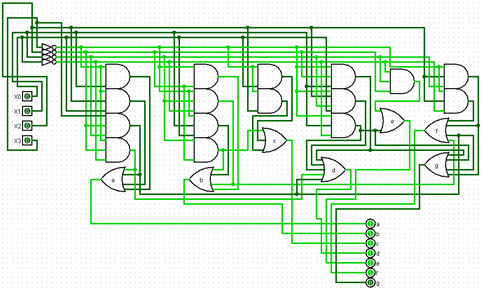

Теперь синтезируем кодер в Logisim (рис. 6). Примечание: в некоторых минимизированных функциях есть одинаковые конъюнкции, в Logisim все идентичные заменяем одной.

Рисунок 5. Результат действий в LogicAid

Рисунок 6. Схема кодера

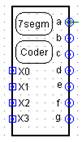

Создаем аналогично двоично-десятичному счётчику библиотечный элемент под названием “Decoder for 7segm” (рис. 7), хотя правильнее будет “Coder”.

Рисунок 7. Внешний вид элемента «Кодер»

Соотнесение входов и сегментов семисегментника в Logisim можно найти в Справка – Справка по библиотеке – Библиотека Ввод/Вывод – 7-сегментный индикатор. Точку “dp” не кодируем, так как ее лучше включать отдельно из-за многоразрядности чисел.

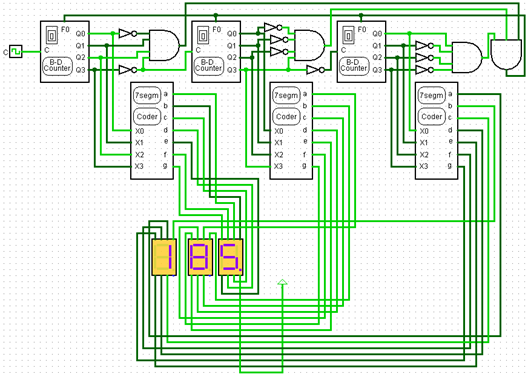

Синтез делителя частоты:

Триггеры внутри двоично-десятичных счётчиков были соединены по Q в C, но в Binary-decimal counter нет выхода Q, зато есть Q3, что является инверсией Q выхода последнего внутреннего RS-триггера, поэтому при синтезе делителя частоты в Logisim счётчики должны быть соединены по Q3 через инвертор (рис. 8).

Рисунок 8. Конечная схема

Выходы счётчика некоторого разряда соединены со входами соответствующего кодера, с кодера сигналы поступают на индикаторы. У последнего семисегментника к точке “dp” подведен постоянный сигнал высокого уровня.

На выходах каждого двоично-десятичного счётчика реализован минтерм через «И» и инверторы, единичный набор которого равен двоичному представлению цифры в 1-м, 2-м или 3-м разряде числа 186 в зависимости от того, какой разряд считает счётчик. Выходы вышеописанных логических «И» поступают на еще одно «И», а затем на входы сброса всех счётчиков F0. Так осуществлено деление на 186.