РАЗРАБОТКА ГЕНЕРАТОРА СИГНАЛОВ ПРОИЗВОЛЬНОЙ ФОРМЫ ТАБЛИЧНЫМ МЕТОДОМ В ПРОГРАММНОЙ СРЕДЕ QUARTUS

Журнал: Научный журнал «Студенческий форум» выпуск №43(179)

Рубрика: Технические науки

Научный журнал «Студенческий форум» выпуск №43(179)

РАЗРАБОТКА ГЕНЕРАТОРА СИГНАЛОВ ПРОИЗВОЛЬНОЙ ФОРМЫ ТАБЛИЧНЫМ МЕТОДОМ В ПРОГРАММНОЙ СРЕДЕ QUARTUS

DEVELOPMENT OF AN ARBITRARY-FORM SIGNAL GENERATOR BY A TABULAR

Bakhtiyar Kusainov

Student, Department of Communications and Information Security, Omsk State Technical University, Russia, Omsk

Grachev George

Student, Department of Communications and Information Security, Omsk State Technical University, Russia, Omsk

Аннотация. В данном курсовом проекте произведено разработка и проектирование устройства генерации сигнала табличным методом на ПЛИС при помощи программной среды Quartus на языке описания аппаратуры Verilog.

Abstract. In this course project, the development and design of a signal generation device by a tabular method on an FPGA using the Quartus software environment in the Verilog hardware description language was carried out.

Ключевые слова: Генератор, аналоговые сигналы, цифровые сигналы, ПЛИС, Quartus, Программируемая логическая интегральная схема, проектирование, Verilog.

Keywords: Generator, analog signals, digital signals, FPGA, Quartus, Programmable logic integrated circuit, design, Verilog.

Инновационные методы решения экологических проблем существуют.

В Verilog память – это массив регистров. Объявляется следующим образом: reg [7:0] mem_name[1023:0]; «mem_name» память, которая содержит 1024 ячеек, каждая ячейка состоит из 8-битного регистра.

Доступ к отдельной ячейке осуществляется так: dac1_d <= mem_name[124] – 8-ми битное значение из 124-ой ячейки записывается в 8- битный регистр dac1_d.

Доступ к отдельному биту ячейки осуществляется так: assign led[0] <= mem_name[124][7] – Значение старшего (7-го) бита 124-ой ячейки назначается 0-му биту шины led.

Доступ к группе бит ячейки осуществляется так: assign led <= mem_name[124][7:4] Значение четырех старших бит 124-ой назначается шине led.

Память может быть инициализирована начальными значениями с

помощью системных функций readmemh и readmemb. При компиляции проекта функции считывают значение из текстового файла и помещают их в указанную память. Файл для функции readmemh должен содержать данные в шестнадцатеричном формате, для функции readmemb – в двоичном.

Вызов функций должен происходить в блоке инициализации Inicial.

Общий синтаксис вызова следующий: $readmemh ( " file_name " , memory_name [ , start_addr [ , finish_addr ] ] ); где file_name – относительный путь к файлу и имя, memory_name – имя инициализируемой памяти, start_addr – начальный адрес для загрузки, finish_addr – конечный адрес. Последние два параметра опциональны.

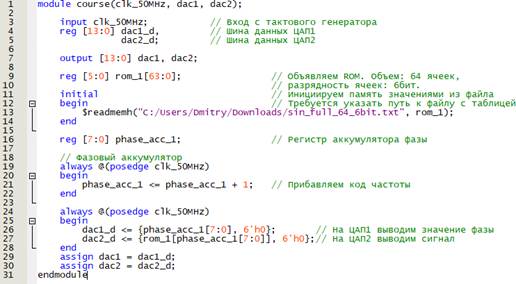

Программный код генератора, а также табличные значения в текстовом файле показаны на рисунке 1 и 2.

Рисунок 1. Программный код генератора

Рисунок 2. Текстовый файл с значениями

На 11 строчке кода происходит чтение текстового файла, в котором записаны 64 отсчета по 6 бит. Данные значения заносятся 6 битный массив регистров rom_1 на 64 ячейки.

По каждому положительному перепаду генератора CLK происходит инкрементация регистра фазового аккумулятора, а также внесение в регистры dac1_d и dac2_d значений. Регистр dac1_d формирует синусоидальный сигнал, dac2_d – пилообразный.

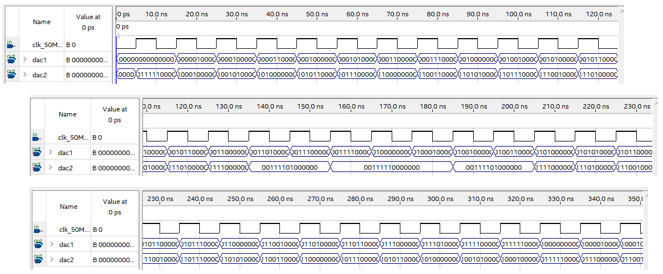

С помощью встроенных инструментов произведена симуляция проекта (рисунок 3).

Рисунок 3. Симуляция работы программы

Заключение

Генераторы сигнала являются неотъемлемой частью современной цифровой индустрии. В ходе выполнения курсового проекта были изучены различные способы генерации сигналов, а также виды генераторов.

В программной среде Quartus разработан работоспособный образец генератора сигнала табличным методом, задаваемый в отдельном текстовом файле. Устройство способно генерировать сигнал с 64 отсчетами на период с 6 битной точностью.