РАЗРАБОТКА УСТРОЙСТВА «ГЕНЕРАТОР ПИЛООБРАЗНОГО СИГНАЛА» В ПРОГРАММНОЙ СРЕДЕ QUARTUS

Журнал: Научный журнал «Студенческий форум» выпуск №43(179)

Рубрика: Технические науки

Научный журнал «Студенческий форум» выпуск №43(179)

РАЗРАБОТКА УСТРОЙСТВА «ГЕНЕРАТОР ПИЛООБРАЗНОГО СИГНАЛА» В ПРОГРАММНОЙ СРЕДЕ QUARTUS

DEVELOPMENT OF THE DEVICE "SAWTOOTH SIGNAL GENERATOR" IN THE QUARTUS SOFTWARE ENVIRONMENT

Vladislav Kemsky

Student, Department of Communications and Information Security, Omsk State Technical University, Russia, Omsk

Аннотация. В данной работе проведена разработка и проектирование устройства генератора пилообразных сигналов на ПЛИС при помощи программной среды Quartus на языке описания аппаратуры Verilog.

Abstract. In this paper, the development and design of a device for a sawtooth signal generator on an FPGA using the Quartus software environment in the Verilog hardware description language is carried out.

Ключевые слова: генератор сигналов, электрические сигналы, преобразователь кода, ПЛИС, Quartus, Программируемая логическая интегральная схема, проектирование, Verilog.

Keywords: signal generator, electrical signals, code converter, FPGA, Quartus, Programmable logic integrated circuit, design, Verilog.

Суть устройства заключена в том, чтобы выдать на своем выходе бинарную последовательность, которая соответствует определенному уровню сигнала. Затем этот сигнал подается на цифро-аналоговый преобразователь, после чего на выходе ЦАП будет получен требуемый сигнал (в данном случае – пилообразный).

Принцип реализации такого генератора основан на переполнении регистра, содержащего уровень сигнала. На вход устройства подаются прямоугольные импульсы (вход clk), по положительному фронту которых производятся действия над регистром. Использован 3-х битный регистр, что позволит выдавать 8 уровней сигнала, к которому с каждым фронтом clk прибавляется 1 (операция инкремент). К тому моменту, когда в регистр будет записано бинарное значение 111, при следующем импульсе произойдёт переполнение, что приведёт к обнулению значения в регистре. Таким образом формируется ступенчатый пилообразный сигнал.

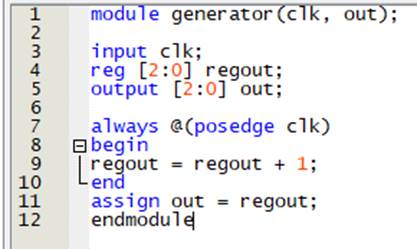

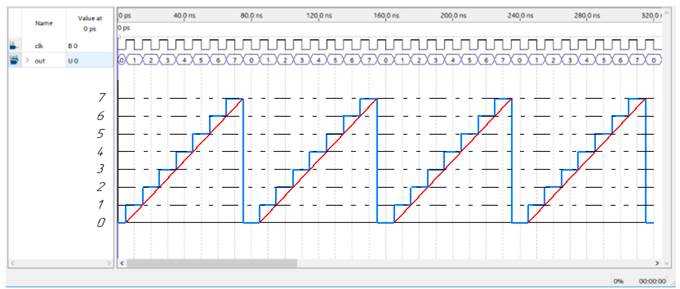

Программный код на языке Verilog HDL представлен на рисунке 12. Функциональная симуляция с наглядным отображением выходного сигнала показан на рисунке 13 (сигнал на выходе устройства – синего цвета, сигнал на выходе ЦАП – красного цвета).

Рисунок 1. Программный код устройства

Построчные комментарии к работе кода:

1 – определение модуля и портов;

3 – определение порта clk, как вход;

4 – определение 3-х битного регистра regout;

5 – определение 3-х битного порта out, как выход;

7 – блок always определяет, по какому сигналу производятся операции внутри него (в данном случае по положительному перепаду волны порта clk);

9 – операция инкремента;

11 – присвоение значения регистра regout выходному порту out;

12 – конец модуля.

Рисунок 2. Симуляция работы кода

Заключение

В ходе выполнения курсовой работы были изучены различные виды электрических сигналов, их отличия и сферы использования. Также изучены генераторы данных сигналов, после чего разработан генератор пилообразных импульсов, основанный на переполнении регистров. На выходе устройства генерируется бинарная последовательность, которая затем подается на вход ЦАП, который преобразует бинарную последовательность в аналоговый сигнал соответствующего уровня.